Abstract: Aiming at the real-time data acquisition requirements of software GPS receiver, a GPS real-time data acquisition scheme based on TMS320C6416 McBSP, EDMA, interrupt and external extended SDRAM is proposed. The hardware receiving circuit composed of RF front-end NJl006AK and TMS320C6416 is mainly described, as well as McBSP. Acquisition and configuration process of SDRAM and EDMA ping-pong buffer. The solution not only satisfies the demanding real-time requirements of GPS software receiver signal acquisition, but also enhances the real-time processing capability of the processor.

Keywords: GPS; real-time data acquisition; multi-channel buffer serial port; EDMA; TMS320C6416; NJ1006AK

This article refers to the address: http://

Introduction Software GPS receivers have high flexibility and scalability, and are an important means to quickly implement algorithm verification and prototype receivers. Real-time acquisition of GPS signals is a prerequisite for the implementation of various functions of software GPS receivers. This paper designs a real-time signal acquisition scheme for software GPS receivers. The scheme uses the McBSP to receive the digital front end NJl006AK digital output, and drives the EDMA in the external expansion sDRAM to buffer the ping-pong buffer through the McBSP event, and synchronizes the data with the baseband algorithm through the ms interrupt (ie, 1 ms interruption), which satisfies the software GPS well. The need for receiver signal acquisition.

1 DSP-based real-time acquisition scheme As a typical application of software radio, software GPS receiver has high data sampling rate and huge computational load brought by baseband algorithm. The tracking link also requires real-time continuous sampling of GPS signals. This requires real-time operation of the processor at the same time, the GPS signal is a high speed, continuous, real-time acquisition. Software GPS receiver operation is mainly realized by the DSP, TMS320C6416 use herein as the core processor, while providing support for baseband processing, using its McBSP, EMDA, the EMIF chip peripherals, and with Nemerix related companies NJ10-06AK the interface circuit completion of the GPS signal in real time, continuous acquisition, which is shown in Figure 1.

The 1 575.42 MHz GPS signal from the antenna directly enters the NJl006AK integrated with the LNA, completes the filtering, amplification and down-conversion of the RF signal, digitizes the 2-bit parallel data, and enters the TMS320C6416 through the parallel-serial conversion circuit. TMS320C6416 McBSP and EDMA by fitting the data move is completed, the stored data is completed by the EMIF interface extension SDRAM. McBSP received serial data into successive 32-bit words and each 32-bit word reception is complete, the completion of 32-bit word received to move by external expansion SDRAM McBSP receive event trigger EDMA. In order to ensure continuous reception and synchronization of real-time data, the McBSP receives event correspondence. The EMDA channel opens up two 1 ms data space buffers in the SDRAM and is configured as a ping-pong buffer operation through the link. When a buffer shift operation ends, the EDMA switches to another buffer and issues an EDMA interrupt, notifying the CPU that the data acquisition is complete, and the acquisition data is synchronized with the baseband processing.

2 system hardware design

2.1 RF Receiver Circuit NJl006AK is a dual superheterodyne GPS RF front-end receiver chip from Nemerix. It integrates an LNA internally, has a local oscillator frequency that can be set via a pin, and can be directly interfaced to an active or passive antenna. The NJl006AK is equipped with a passive antenna to complete the reception and processing of the RF signal. The circuit is shown in Figure 2.

By passive antenna L1, C1, C3, L5 GPS signal is coupled into the interior NJl006AK integrated LNA, low noise amplification; LNO by entering the pin L2, L3, L4, C2, C4 and SAW oscillator configured TQS949-AA-7G The filter circuit completes the filtering of the GPS L1 out-of-band signal. NJl006AK is grounded through the MODE pin to select the local oscillation frequency of 1 554.86 MHz, which is mixed with the filtered signal entered by the RFI pin to complete the down conversion to obtain the 20.55 MHz IF signal. The intermediate frequency signal is amplified by the internal AGC by the NJl006AK, and then subjected to secondary down-conversion by the under-sampling of the 2-bit ADC to output the SGN and MAG digital signals. The ADC reference clock is grounded through the XEN pin to select the 16.129 MHz sample clock supplied by the CP pin input to the baseband interface. In addition, L6, L7, C6, and C9 form a filter circuit centered at 25.55 MHz with a bandwidth of 3.5 MHz to filter out the image frequency introduced during A/D conversion; R1, C7, and C10 form the internal PLL of NJl006AK. External filter circuit; AVDD, TVDD provide 3.3 V working voltage for NJl006AK; C5, C8 complete the filtering of the output voltage of NJl006AK on-chip to prevent internal reference offset of the chip.

2.2 parallel string conversion and storage interface circuit Parallel conversion and external SDRAM storage interface circuit shown in Figure 3.

The 50 MHz temperature-compensated crystal oscillator provides clock input to the TMS320C6416 through CLKIN, and the internal PLL of the CLKMODE0 and CLKMODE1 pull-ups is 20 times the frequency, allowing the processor to operate at 1 GHz. McBSP0 provides parallel and serial conversion to the SN54LV166A interface while providing the sampling clock CLKF to the RF front end. EMIFA is in 32-bit form with Microm Corporation 64. Mb 32-bit SDRAMMT48LC2M-3282-6 docking for external storage expansion.

In the parallel-serial conversion interface, the CLR pin of the SN54LVl66A is connected to 3.3 V to disable asynchronous clearing; the S/L pin is grounded to select the parallel input mode, and the A to H parallel input is received; the INH pin is grounded to enable the CLKR provided by McBSP0. The shift clock; the digital signals SGN and MAG from the RF front end are sequentially received by the QH output to the McBSP0 on the rising edge of CLKR.

External expansion SDRAM configuration in EMIFA CE0 space, BEAl6 pull-down, BEAl7 pull-up set CPU internal divide-by-6, AECLKOUTl output 166 MHz and MT48LC2M3282-6 CLK docking, other control signals ASDCKE, ACE0, AS-DRAS, ASDCAS, ASDWE, AEA [13:3], ABE E3: O], AEDE31: O] directly connected to the signal corresponding to MT48LC2M3282-6. Due to the SDRAM multiplexed address lines, A11~A18 of MT48LC2M3282-6 are multiplexed with A0~A7, and BA0 and BAl provide group selection signals as A19 and A20. Therefore, A0~AAl3 of TMS320C6416 is connected to A0~A10 of MT48LC2M3282-6 to complete A0~ For the transmission of A18, AEE4 and AEAl5 are connected to BAl and BA0 to provide a group selection signal.

3 acquisition parameter configuration

3.1 McBSP Receive Configuration McBSP is responsible for receiving the RF front-end sampled signal. The receive configuration is divided into clock generation settings and receive parameter settings. Its control parameters are mainly distributed in the interface control register, the receive control register, the pin control register and the sample rate register. The Pin Control Register and Sample Rate Register provide flexible frame signal and clock generation for the McB-SP, either by external pin input or by internal clock divider, while providing polarity reversal control for output to external pins. In this scheme, set the sampling rate register CLKSM=1, CLKGDV=30, FPER=1, FWID=0, so that the internal 1 GHz clock of McBSP0 is divided by CLKGDV to obtain the 32.258 MHz receiving clock required for internal reception, and then pass The frame signal period FPER and the frame pulse width FWID are divided to generate a frame signal with a duty ratio of 50% at 16.129 MHz. At the same time, set CLKRM=1, CLKRP=0, FSRM=1, FSRP=1 in the pin control register, so that the frame signal with polarity inversion is output to the FSR pin (the falling edge is used for GPS signal sampling and completion of the RF front end). Receive frame synchronization), the receive clock is directly output to the CLKR pin (its rising edge is used for the serial-to-parallel conversion circuit to complete the data shift output, and the falling edge is used for the McBSP to sample the external data).

The receiving control register and the interface control register mainly provide control functions such as receiving frame length, word length, frame ignoring, receiving delay, clock, frame occurrence, and reception start. In order to improve the efficiency of McBSP0 and EDMA as much as possible, set RPSASE=0, RFRLENl=1, RWDLENl=5, RDA DLY=0, RFIG=1 in the receive control register. Each frame is selected to contain one phase, each phase containing one word, 32 bits per word, synchronized with the frame signal without delay sampling reception, and ignoring inappropriate frame synchronization. After setting the above registers, the sampling rate generator reset can be completed by setting GRST, FRST and RRST in the interface control register to 1, and the frame signal generator reset and receiving enable to start receiving.

3.2 EMIF SDRAM Interface Configuration The EMIFA CE0 space-expanded 64 Mb SDRAM is located in the CPU address space 0x8000 0000~0x807F FFFF, which provides a cache for the signal acquisition process. The configuration information is distributed in the EMIFA global control register, the CE control register 0, the SDRAM control register, the SDRAM time parameter control register, and the SDRAM extension register. After the reset is completed, the CPU needs to configure the necessary parameters according to the EMIFA register, and then start the SDRAM initialization process to make the SDRAM enter the normal read and write state.

The 166 MHz synchronous clock required for SDRAM operation is enabled by setting the EMIFA global control register EKlEN=1. At the same time, set MTYP=0x03 in CE control register 0 and select CE0 as 32-bit SDRAM mode. The SDRAM working refresh period in EMIFA is realized by 166 MHz synchronous clock counting. In the SDRAM time parameter control register, PERIOD is set to 2 500, that is, 2 500×(1/166 MHz)≈1.51μS for refresh operation, the specific refresh times. It is set to be once every 1.51 μs by XRFR=0. The SDRAM extension register provides the time parameter settings required for SDRAM operation. The specific settings are: TCL=1, TRAS=5, TRRD=0, TWR=1, THZP=2, RD2RD=0, RD2DEAC=2, RD2WR=0, R2WDQM=2, WR2WR=0, wR2DEAC=4, WR2RD= 0. The SDRAM control register is set according to the device parameters SDBSZ=1, SDRSZ=0, SDCSZ=1, which in turn indicates that the number of addressed banks is 4, the row address is 11 bits, and the column address is 8 bits. At the same time, three key time parameters Trcd=2, Trp=2, and Trc=8 are set. After the CPU completes the above parameters after resetting, the external SDRAM can be initialized by writing a 1 to the SDRAM control register INT bit.

3.3 EDMA Ping Pong Cache and Interrupt Configuration EDMA works with event-driven mechanism. Each McBSP receives the completion event REVT to drive EDMA, and completes the transfer of the McBSP DRR register to the external extended SDRAM. in

In the TMS320C6416, the McBSP0 receives the completion event REVT corresponding to the EDMA channel 13. The RAM parameter of the ping-pong buffer mode needs to be set first, and then the interrupt and the corresponding channel are enabled to enter the ping-pong working state waiting for the trigger event, and the data is synchronized with the processor by the interrupt.

The RAM parameters of the EDMA channel include: channel parameter OPT, source address SRC, frame count CNT, target address DST, target address index IDX, and five consecutive 32-bit control words that link the loaded RLD. Among them, OPT sets the transmission mode, SRC sets the source address of data transmission, CNT sets the number of frames and the number of intra-frame transmission units, DST sets the destination start address for transmission, IDX sets the destination address correction parameters, and RLD settings. The link RAM parameter is offset from the starting address of 0x01A0 000.

To implement ping-pong buffering on channel 13, you need to use two reloadable RAM parameter blocks A, B at 0x01A00600 and OxOlA0 0618, and 2 buffers BUFl at external SDRAM Ox8000 0000~0x8000 0FBF and 0x8000 1000~0x8000 1FBF. And BUF2. Set A DST=0x8000 0000 to BUFl, RLD=0x0000 0618 to RAM parameter block B, B DST=0x8000 1000 to BUF2, RLD=0x0000 0600 to RAM parameter block B, and set LINK in OPT in each RAM block Control bit. Thus, when the last cell transfer of the A RAM block ends, the B RAM block parameters pointed to by the RLD are automatically loaded. When the next trigger event arrives, the EDMA will move the data to the BUF2 pointed to by the Ox8000 1000. On the contrary, when the last cell transfer of the B RAM block ends, the ARAM block parameter pointed to by the RLD will be automatically loaded to move the subsequent data to the BUF1 to implement the ping-pong buffer. In addition, the OPT of RAM parameter blocks A and B is set to Ox0002 0002, which enables channel 13 to operate in the 32-bit one-dimensional element synchronous link mode of the highest priority fixed address to the incremental address. SRC is set to McBSP0 DRR address 0x018C 0000, CNT is set to Ox0000 03FO for 1008 words of single frame transmission, IDX does not affect the synchronous transmission of one-dimensional elements, set to Ox0000 0000.

In order to maintain the synchronization of McBSP and EDMA operations, all EDMA-INTs shared by ED-MA channels are mapped to maskable interrupt INT_8 by MXL[25:21] before channel 13 is enabled, and ICR Bit8 is set to clear all pending. Interrupt, set IER Bitl, Bit8 enable NMI and INT_8, and finally set global interrupt enable GIE. When channel 13 is enabled, the EDMA event clear register ECRL and the interrupt pending register CIPRL Bitl3 must be set first to clear the previously occurring McBSP0 REVT event and the pending interrupt signal; then the EDMA interrupt enable register CIERL and channel are set in turn. Enable register EERL bitl3 to enable channel 13 and the corresponding interrupt.

4 Acquisition process analysis The GPS signal acquisition scheme based on McBSP, EDMA and SDRAM is mainly divided into two stages: interface configuration and signal acquisition. The interface configuration phase completes the EMIFA, EMDA, interrupt, and McBSP0 configurations in sequence, allowing them to operate in a certain mode of operation. Finally, the acquisition process is initiated by setting RRST in the McBSP interface control register. The signal acquisition process is based on hardware implementation and is completely concurrent with the CPU. After the ms data is received, the CPU synchronizes the data with the interrupt INT_8. The specific acquisition process is shown in Figure 4.

The McBSP32.258 MHz receive clock receives a 32-bit word for 32 consecutive falling edges, producing a REVT event corresponding to 16 falling edges of the 16.129 MHz RF sample clock. The REVT event drives the EDMA to complete a DRR 32-bit receive data transfer to the SDRAM buffer, and decrements the CNT by one, and the buffer address plus 4 points to the next buffer location. Assuming that EDMA is currently performing RAM parameter A transmission, then 32.258 MHz receive clock has 32 258 falling edges in 1 ms, and can receive 1008 32-bit receive data, generating 1008 REV events; corresponding to 16.129 MHz sample clock 16 128 The next falling edge sampling, the total drive EDMA 1008 32-bit shift, occupying BUFl Ox8000 0000 ~ 0x8000 0FBF 4 032 bytes space, CNT reduced to O. Once the CNT is reduced to O, the EDMA triggers INT_8 to notify the CPU that the data acquisition is complete. At the same time, according to the RLD setting, the parameter RAM B at 0x01A0 0618 is loaded to the self-parameter RAM of channel 13. When the next REVT event arrives, the EDMA performs the RAM parameter B transmission and buffers it in the Ox8000 1000~Ox8000 1FBFBUF2. At this time, the CPU can process the collected data in the BUF1. When the CNT is again reduced to 0, the EDMA triggers INT_8 again to notify the CPU that the data acquisition is completed. At the same time, the parameter RAM A at the 0x01A0 0600 is loaded to the channel 13 according to the RLD setting to implement the ping-pong buffer. It should be noted that McBSP RFIG=1 works in the frame ignore mode, and the subsequent synchronization signal is ignored after the synchronization of the first CLKF falling edge is completed, until the end of the 32-bit frame can achieve the next frame synchronization.

Conclusion The GPS real-time signal acquisition scheme based on NJl006AK and TSM320C6416 proposed in this paper makes full use of DSP internal peripherals, and has the characteristics of simple and reliable circuit, flexible configuration method and concurrent CPU synchronization. The scheme solves the problem of real-time data acquisition and baseband processing real-time conflict in software GPS receiver, and realizes real-time and continuous acquisition of GPS signals, which is of great significance for improving the real-time performance of software GPS receivers.

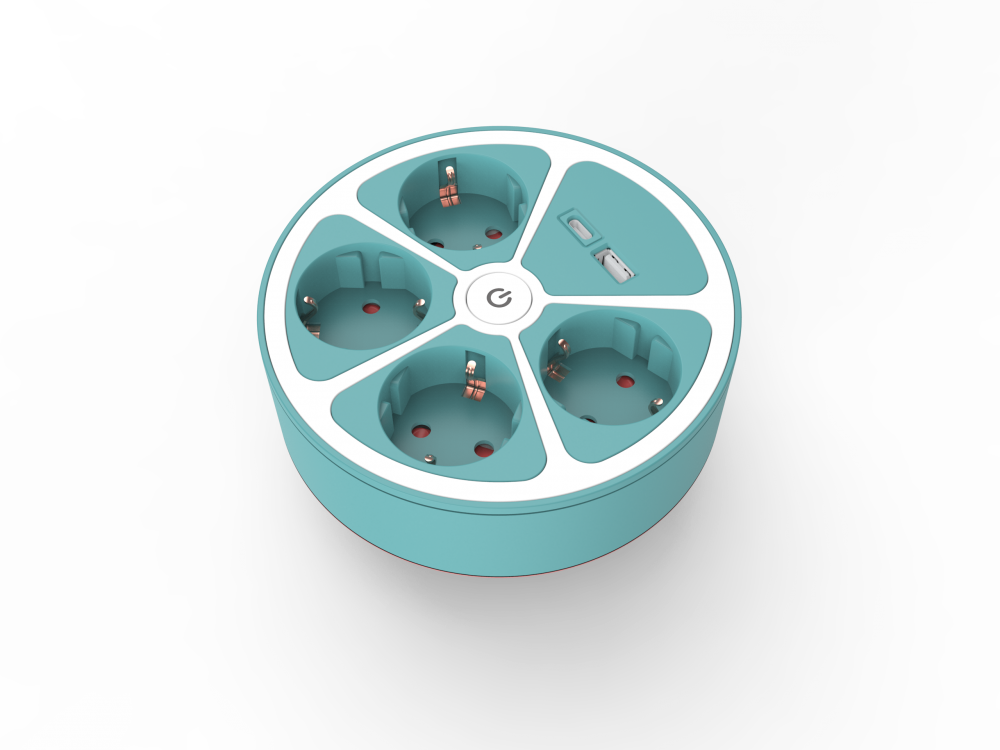

Germany Type Electronics Connection

Germany power strips distrbute power to multi devices, computer, refrigerator, etc at same time. The dural plastic housing(flame retadent PP merterial) stands 750 degree high temperature, children safety shutter, premium safety for you and your family. Right-angle plug type E can be flexibility used for suers and save space at same time. The KYFEN Germany USB power strips with USB type A or type C, deliver power to moblie phone, game machine or other mobile machine. KYFEN Germany extension cord socket got CE/GS/RoHS/REACH approved, comply with eu sales requirements.

Germany Type Electionics Connection,Power Strips,Power Extension,Power Distribution Unit

CIXI KYFEN ELECTRONICS CO.,LTD, , https://www.kyfengroup.com